Class: XIIth

Date:

**Solutions**

**Subject: PHYSICS**

**DPP No.: 2**

## **Topic:** - semiconductor electronics: materials, devies and simple circuits

1 **(b)**

$$\overline{A \cdot A} = \overline{A} + \overline{\overline{A}} = \overline{A} + A = 1$$

$$A \cdot \overline{A} = 0$$

$$A + \overline{A} = 1$$

$$A + 1 = 1$$

2 **(b)**

The conductivity of an intrinsic semiconductor decreases with decrease in temperature and so it behaves as an insulator at 0 K. The conductivity of an insulator is zero. Therefore, the electrical conductivity of an intrinsic semiconductor at 0 K is equal to zero.

5 **(c)**

When a p-n junction is formed, n-side attains positive potential and p-side attains negative. When ends of p and n of a p-n junction are joined by a wire, there will be a steady conventional current from n-side to p-side through the wire and p-side to n-side through the p-n junction.

6 **(c)**

Wood is non-crystalline

7 **(c)**

At ordinary temperature  $n_e = n_h$ .

8 **(d)**

As shown, we conclude that *A* and *C* are analogue signals but *B* is digital signal.

9 **(b**)

In reverse biasing, width of depletion layer increases

10 **(c)**

$$R_p = \frac{V_p}{i_p} = \frac{50}{150 \times 10^{-3}} = 333.3 \,\Omega$$

11 **(b)**

$$V_b - i_b R_b \Rightarrow R_b = \frac{9}{35 \times 10^{-6}} = 257 \ k\Omega$$

12 **(d)**

In forward biasing both  $V_B$  and x decreases

13 **(a)**

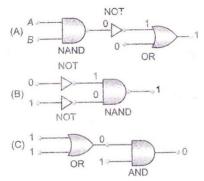

Truth table for given combination is

| A | В | X |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

This comes out to be truth table of OR gate.

14 (c

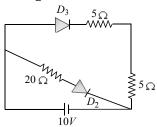

In the given circuit, diode  $D_1$  is reverse biased, so it will not conduct. Diodes  $D_2$  and  $D_3$  are forward biased, so they will conduct. The corresponding equivalent circuit is as shown in the figure

The equivalent resistance of the circuit is

$$R_{eq} = \frac{(5+5) \times 20}{(5+5) + 20} = \frac{10 \times 20}{10 + 20} = \frac{200}{30} = \frac{20}{3} \Omega$$

Current through the battery,  $I = \frac{10V}{\frac{20}{3}\Omega} = 1.5A$

16 (c

If the voltage of the DC source is increased then both conductor and semiconductor registers same current *ie*, semiconductor is in forward biased condition and it conducts. So, ammeters connected to both semiconductor and conductor will register the same current.

17 **(b)**

The temperature coefficient of resistance of silicon (*ie*, semiconductor) is negative and that of platinum (*ie*, conductor) is positive.

18 **(c)**

In forward biasing of *PN* junction diode width of depletion layer decreases. In intrinsic semiconductor fermi energy level is exactly in the middle of the forbidden gap

20 **(a)**

The output gate circuit will be as shown below.

Hence, outputs of *A*, *B* and *C* are 1, 1, and 0 respectively.

| ANSWER-KEY |    |    |    |    |    |    |    |    |    |    |

|------------|----|----|----|----|----|----|----|----|----|----|

| Q.         | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

| A.         | В  | В  | С  | С  | C  | С  | С  | D  | В  | С  |

|            |    |    |    |    |    |    |    |    |    |    |

| Q.         | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| A.         | В  | D  | A  | С  | D  | С  | В  | С  | С  | A  |

|            |    |    |    |    |    |    |    |    |    |    |